# EFLX® Embedded FPGA

Dense, Fast, Proven, Scalable

# **Everything You Need for an eFPGA in Your SoC**

- ✓ High density & high performance similar to commercial FPGA

- ✓ eFPGA Arrays of any size by tiling proven eFPGA IP Logic and/or DSP tiles

- ✓ Compatible with most metal stacks. Integrate RAM between tiles

- ✓ Silicon proven in TSMC 12/16, 28, 40 & GF 12 with evaluation boards

- √ -40 to +125C Tj. Compatibility with your metal stack and your voltage range

- ✓ Software tools with a Graphical User Interface

- ✓ Timing files extracted from design database and available across all corners

- ✓ High DFT fault coverage with special logic for 100x acceleration of test time

- ✓ Software, applications and physical design experts will support your design

#### First eFPGA TSMC IP Alliance Member

Flex Logix® is a TSMC IP Alliance Member based on the work it has done with TSMC over many years to develop embedded FPGA IP meeting TSMC9000 compliance for design methodology, validation in silicon & documentation. Flex Logix will continue to prove all EFLX® embedded FPGA IP in silicon with rigorous engineering checks and sign-offs.

#### TSMC 6/7/12/16/28/40, GF 12/22, Sandia 180

| TSMC N7/N6                  | EFLX 4K         | In Design; available |

|-----------------------------|-----------------|----------------------|

| TSMC 12FFC/+/16FFC/+/FF+    | EFLX 4K         | PROVEN IN SILICON    |

| TSMC 12FFC/+/16FFC/+/FF+    | nnMAX Inference | PROVEN IN SILICON    |

| TSMC 28HPC/HPC+             | EFLX 4K         | PROVEN IN SILICON    |

| TSMC 40ULP/LP               | EFLX 1K         | PROVEN IN SILICON    |

| Global Foundries 12LP/12LP+ | EFLX 4K         | PROVEN IN SILICON    |

| Global Foundries 12LP/12LP+ | EFLX 4K RHBD    | PROVEN IN SILICON    |

| Global Foundries 22FDX      | EFLX 4K         | In Design; available |

| Sandia 180                  | EFLX 4K         | PROVEN IN SILICON    |

Detailed product briefs are available for each EFLX core. Operating temperature range is -40C to +125C Tj. Multiple voltage ranges are supported. The EFLX Compiler has timing at numerous corners for each core.

We can port to other process nodes in ~6-8 months when resources are available: check with Sales.

## **eFPGA Adoption is Taking Off!**

Multiple customers have built chips using EFLX eFPGA (>18) and more are in fab and in design (>12) across multiple process nodes and multiple applications.

Customers include Dialog, Socionext, Microsoft, AFRL, Boeing, Morningcore/Datang Telecom, Sandia Labs, DARPA, Harvard, HiPer & many more that are not yet public. ASIC companies with eFPGA experience include GUC, OpenFive and Synapse.

Applications use eFPGA for flexibility and for acceleration in 5G, Networking, Data Center, Wireless, Mixed Signal, MCU, IoT, Automotive, Consumer and Aerospace.

# EFLX Embedded FPGA

# XFLX™, ArrayLinx™ & RAMLinx™ Interconnects

#### **Revolutionary Interconnect Enables Density and Scalability**

Traditional FPGA fabrics are only 20% programmable logic; the programmable interconnect takes 80% of the area!

Flex Logix has developed revolutionary new interconnects:

- 1. **XFLX Interconnect** reduces the programmable interconnect area by *half* AND reduces the number of metal layers required keeping the eFPGA in the lower metal layers. This enables density similar to commercial FPGA and compatibility with most metal stacks.

- EFLX utilization is typically >90%!

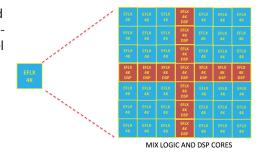

- 2. ArrayLinx Interconnect allows a large number of eFPGA array sizes to be built quickly using a single, silicon proven eFPGA IP core.

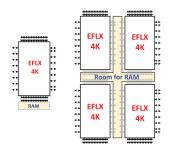

- 3. RAMLinx Interconnect provides any type and amount of BRAM (SRAM) to be quickly interleaved in an eFPGA array using silicon proven eFPGA IP cores.

These interconnects are covered by numerous issued and pending patents in the USA and other countries.

#### **Density & Performance Similar to Full Custom FPGA**

The XFLX interconnect takes  $\sim$ 1/2 the area of traditional FPGA mesh interconnect, so even though we use standard cells for rapid implementation, we achieve density and performance similar to commercial FPGA. And we use only 5-7 metals layers, so we are compatible with most metal stacks.

#### **Embedded FPGAs from 1K to 100Ks LUT4s**

EFLX arrays are constructed from building blocks: the EFLX 1K core with ~1000 LUT4s and the EFLX 4K core with ~4000 LUT4s. They are eFPGAs with programmable logic, programmable interconnect, I/O, clock circuitry and configuration logic. They also have a top level **ArrayLinx Interconnect** which is used to build arrays of larger size by "tiling" into arrays with no GDS change. Arrays can be delivered in days & customers are encouraged to use multiple, different size arrays in a single design. All EFLX cores are proven in silicon in arrays of at least 2x2 so all array sizes are proven out. Arrays up to ~250K LUT4s are available now using EFLX 4K in any mix of Logic/DSP cores and we can scale up to much larger arrays as customers require.

#### **Thousands of Interface Pins**

A single EFLX 4K core has >1000 interface pins: 632 in and 632 out, larger arrays have much more. You can connect EFLX embedded FPGAs into wide, fast buses and wide data and control paths; the interfaces are standard CMOS so they run very fast.

## **Optional MACs for DSP/AI/ML Acceleration**

EFLX cores are offered in DSP versions where some of the LUTs are replaced with Multiplier-Accumulator (MAC) blocks consisting of a 22-bit preadder, 22-bit multiplier and 48-bit accumulator which can be pipelined for very fast DSP implementations. For Al/ML, the multiplier can be configured as two 11x11 multipliers for double the throughput.

#### **Optional BRAM: Any Kind, Any Amount**

The EFLX cores contain memory. If you require more, it can be synthesized at the edge of the array or between the cores, within the array. The EFLX Compiler software will map your RTL onto the BRAM as part of the array. We synthesize RAM from standard compilers with optional MBIST: single port or dual port, whatever size and number of blocks you want, with or without parity/ECC. We can also integrate your special memory like TCAM.

## **Test and Reliability Features**

Test vectors are available with high stuck-at fault coverage for DC and AC coverage. Our Gen 2 Architecture has a special test mode that accelerates test speeds 100x over our first generation. For High Reliability applications we have the ability to read back the configuration bits and "scrubbing" is also possible to re-write configuration bits periodically.

# **EFLX eFPGA Applications**

# SoC, Acceleration, AI/NN Examples

#### Sandia Labs First SoC with eFPGA Working in Sandia 180nm

Flex Logix developed EFLX eFPGA for Sandia for their 180nm Fab: it is Gen 2 EFLX 4K.

At DAC 2018 Sandia Labs presented their implementation and architecture which they will use to build multiple SoCs and described the first SoC fabricated with eFPGA, Dragonfly.

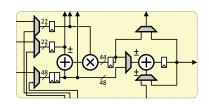

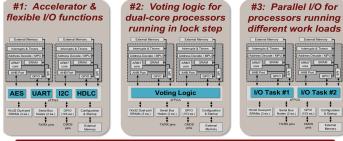

An example of how they can reconfigure the eFPGA in their Dragonfly SoC for different use cases is shown to the right.

#### DragonFly: eFPGA Usage Examples

The eFPGA enables the DragonFly SoC to target multiple applications

#### eFPGA Acceleration

An App Note on our website shows how small eFPGA arrays can accelerate heavy workloads like encryption/decryption (AES, SHA), JPEG Encoding and FFT as examples 30-100x faster than an ARM Cortex M4 processor. Since eFPGA is reconfigurable multiple workloads can be accelerated as needed. Same ASIC, different applications.

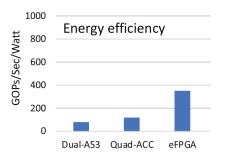

## TSMC 16FFC SoC Shows eFPGA is Low Energy for Al

Harvard implemented a 2x2 EFLX array, 2 DSP and 2 Logic EFLX 4K cores: ~14K LUT4s and 80 MACs. Their paper, presented at HotChips 2018, shows that of the programmable DNN Accelerators they implemented, eFPGA had similar area efficiency but much better energy efficiency.

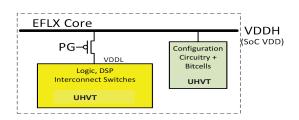

#### Low Power eFPGA

EFLX eFPGA can be optimized for maximum performance OR for low power, in any given process node.

Our new TSMC 40ULP design is optimized for power. Our GF 12LP/LP+ EFLX 4K comes in both a performance optimized version and a version with power manage-

#### Rad Hard eFPGA for Space

For Space applications, we can use Rad Hard Standard Cells for storage elements and design rules for clock lines and resets to improve tolerance to Single Event upsets. Synopsys Premier can be used to triplicate critical logic for further enhancements. Sandia 180 and a version of GF 12LP/LP+ are Rad Hard.

# T16FFC, T28HPC+ & GF12 Evaluation Boards

Evaluation boards are available for TSMC 16FFC, TSMC 28HPC+ and GF 12LP. Bitstreams can be programmed using your Verilog to demonstrate at-speed performance and power. PVT monitors on chip so you can measure chip temperature and voltage. Interfaces to PC over USB.

# **EFLX Embedded FPGA**

# Software, Evaluation Boards, Business

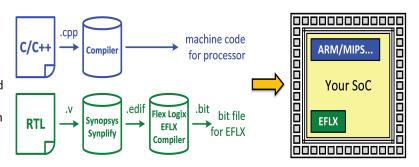

## **EFLX Compiler Programming**

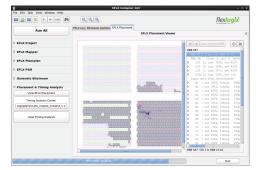

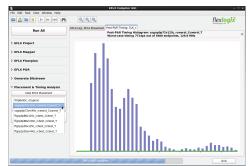

To program the EFLX array, use Synopsys® Synplify to generate an .edif file which is then input to the EFLX Compiler. You also provide an IO file which shows how the EFLX array is connected to the rest of your chip. EFLX Compiler packs, places, routes and iterates to generate optimum timing performance; if it is acceptable, EFLX Compiler generates the bitstream which when loaded into the EFLX array executes your RTL.

#### **Easy to Use GUI**

Our GUI makes array floorplan building and timing path analysis quick and easy. New features are in development as well.

#### **Emulation Models for Cadence and Mentor**

Emulation Models are available for EFLX eFPGA on both the Cadence Palladium Z1 and the Mentor Veloce Strato emulation platforms. These models have been used by us in designing our InferX X1 Al Inference accelerator and by our customers in designing their SoCs. Emulation speeds chip development and enables architectural investigation.

#### **About Flex Logix**

- Our interconnect technology allows us to develop eFPGA that is similar to Xilinx density and speed but in much less time

- Our CEO has managed business units with up to 500 people and taken a startup from 4 people to IPO to \$2 Billion Market Cap

- Our Executives all have extensive industry experience and industry recognition, including the Outstanding Paper Award at ISSCC

- Our technical team is a combination of silicon engineering, software development, architecture & system engineering

- ✓ We have dozens of issued US patents and many many more in application in multiple countries

#### **Well Financed**

We have raised ~\$82 Million; our lead investors are Mithril, Lux Capital and Eclipse Ventures. eFPGA sales are growing and we are now profitable. We have a strong cash balance. We are hiring to keep up with customer needs for eFPGA and Inference.

www.flex-logix.com